For the organic CMOS, the code can be shown as

The result can be shown as:

Explanation:

In silicon semiconductors, the mobility of electron(un) is twice of the mobility of holes. On the other hand, holes mobility is the double of electron mobility in organic semiconductors. The final voltage transfer curves of two kind of transistors are shown in the figure above. It can be observed that there is a shift between two curves. That is to say, when the nMOS and pMOS both saturate, the input voltage of silicon transistor is smaller than the input voltage of organic transistor.

It is known that, with the increase of input voltage, the pMOS goes from linear region into saturation region. Since the nMOS saturates after Vin is larger then Vtn, once the pMOS saturates, both parts saturate. At that input voltage value, the curve falls sharply and seems to be a straight line that perpendicular to the x axis. Because nMOS and pMOS are both saturates, that particular value of input voltage can be derived as:

In this simulation, the aspect ratio does not change and mobility of holes and electrons differs between silicon and organic transistors. Hence  n/

n/ p is un/up, which means the special input voltage is decided by the mobility. Since un/up in organic CMOS is 2 and in silicon is 0.5, the voltage value of organic is larger than silicon. That explain why there is a shift between two curves.

p is un/up, which means the special input voltage is decided by the mobility. Since un/up in organic CMOS is 2 and in silicon is 0.5, the voltage value of organic is larger than silicon. That explain why there is a shift between two curves.

The code for researching the mobility effects on the PMOS can be shown as:

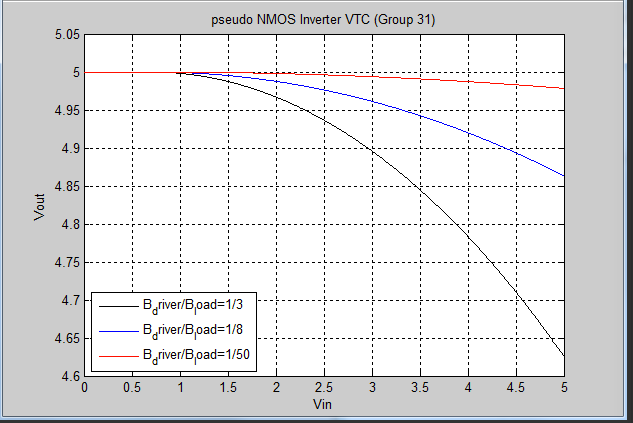

The result that we got :

Explanation:

For a enhancement load n channel MOS, the load transistor gate is connected to the drain,

hence the load is always saturated. When the input voltage applied to the driver transistor is less than Vtdriver, the output voltage is the voltage across load, that is VDD-Vtload.

When input voltage grows larger than Vtdriver, the driver is also saturated and a drain current is induced in to driver transistor. At that region, the output voltage is linear with input voltage. As the input voltage further increases, the driver transistor no longer saturated but the driver and load drain currents are still equal. As a result, the input-output relationship is a curve rather than a straight line. The aspect ratio decides the slope in the driver-saturation region, thus when the aspect ratio increase the line of input-output falls sharper. In addition, when the aspect ratio decreases, the effective resistance increases, hence the minimum output voltage decreases.