This week, we did further research on organic CMOS and PMOS.

According to

the supervisor's suggestion, we need to use MATLAB to simulate the voltage transfer characteristics

curves of organic CMOS and PMOS.

1. Organic CMOS VTC

we try to use MATLAB to simulate the voltage transfer characteristics curve of the organic CMOS. Some parameters are given by the supervisor, which are shown as following.

The hole mobility,up, is given as: 0.0001(m^2)/vs

The electron mobility, un, is given as 0.00005(m^2)/vs

The oxide capacitance, Cox, is 1.66*(10^-4) f/(m^2).

In MOSFET, K is a very important parameter which is known as transistor conduction parameter. Kn is for NMOS and Kp is for PMOS.

where un is electron mobility, up is hole mobility and Cox is oxide capacitance.

Moreover, Cox is given by

where tox is oxide thichness and εox is oxide permittivity, which is given by

Furthermore, k'n and k'p are process conduction parameter. In this case,

k'n=0.0001(m^2)/vs*1.66*(10^-4) f/(m^2)=1.66*10^-9 F/vs

k'p=0.00005(m^2)/vs*1.66*(10^-4) f/(m^2)=8.3*10^-9 F/vs

Then, we use the MATLAB to draw the curve. The code can be shown as :

The curve can be shown as:

In order to find the different conditions in different aspect ratios. The code can be changed as:

Then the curve can be drawn as:

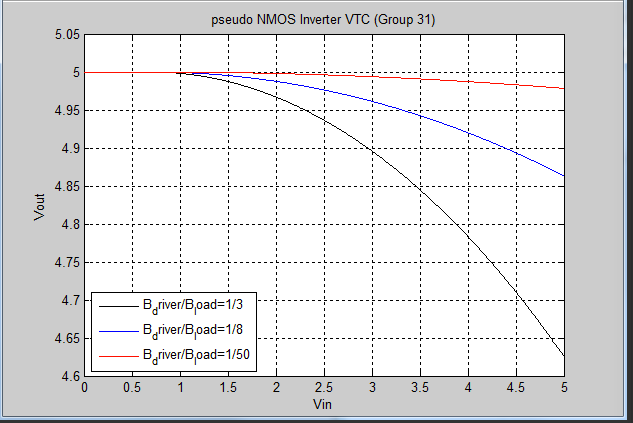

2 PMOS VTC

A pseudo PMOS circuit should be like

for a PMOS, VDD should be -VDD and VDS, VGS should be VSD and VSG.

(1)When Vin < VTD,

driver is cut off and the currents are zero. Hence the maximum output voltage does not reach the full VDD value:

(2)When Vin>VTD,

driver transistor turns on and is biased in the saturation region.

The output voltage can be given as:

The output voltage decreases linearly with Vin.

(3)When Vin>VIt,

Input voltage at the transition point is given as:

When input voltage is larger than VIt, the driver becomes biased in the non-saturation region, and then

The relationship between input voltage and output voltage is no longer linear.

The last VTC should be like

When the aspect ratio is greater than unity, the inverter gain magnitude is greater than unity.

The W/L for load is given as 15um/5um while the W/L for driver is 5um/5um,while changing aspect ratio to other values, the curve can be drawn as:

The code for this process is shown as: